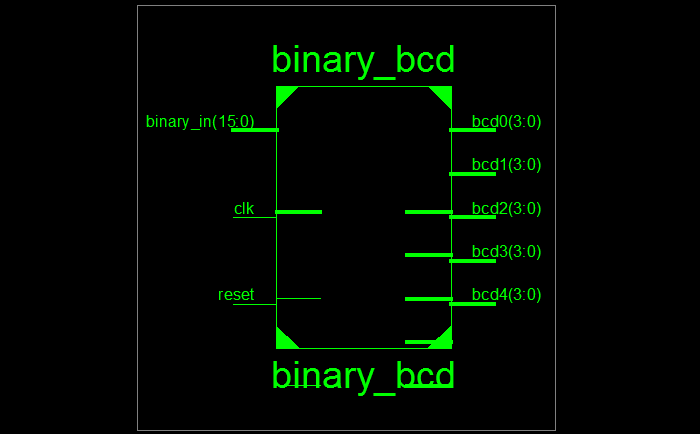

You are required to program a PAL device to design a 64-bit counter. The stated PAL can be programmed using ABEL and VHDL. Which technology would you use to accomplish the task

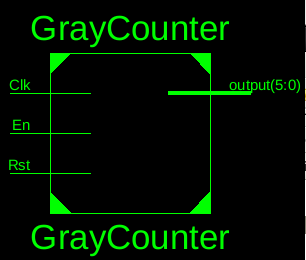

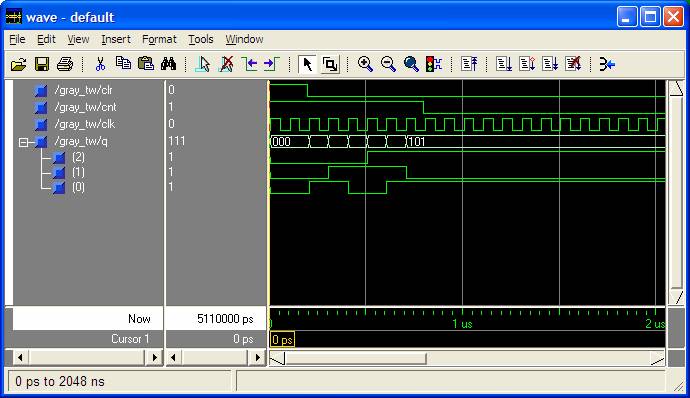

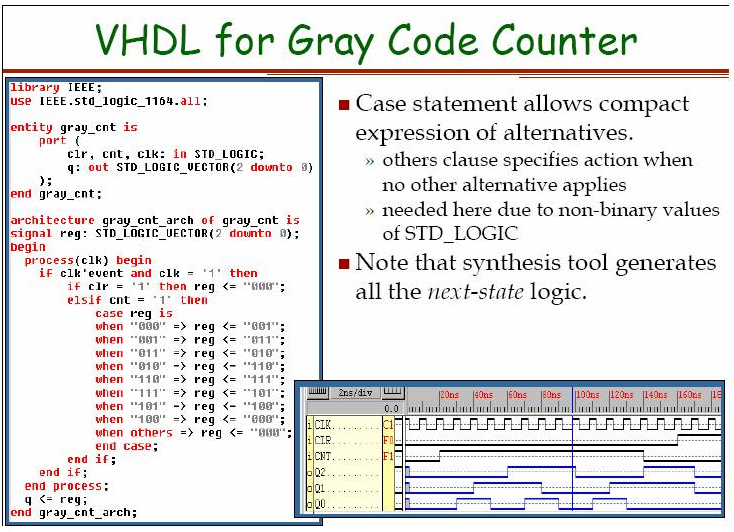

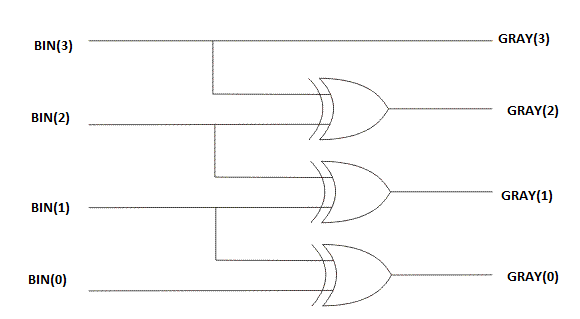

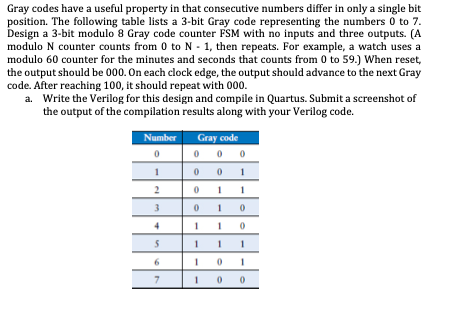

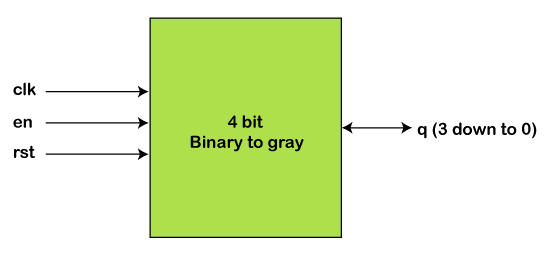

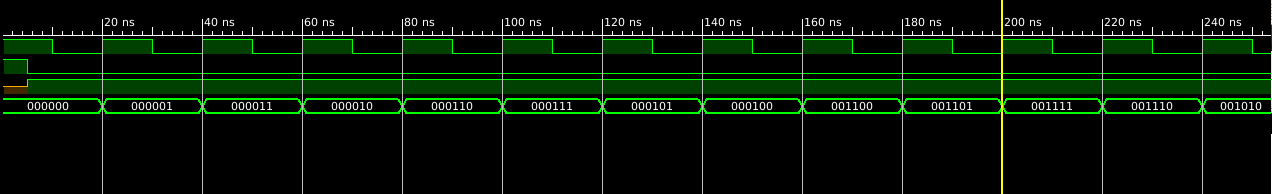

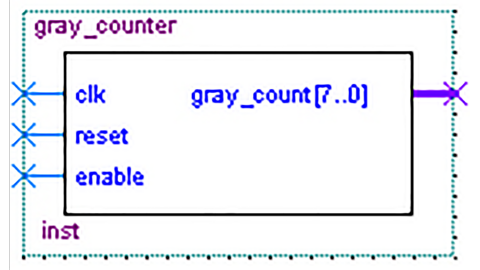

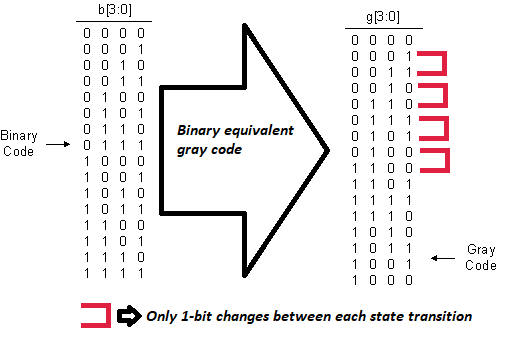

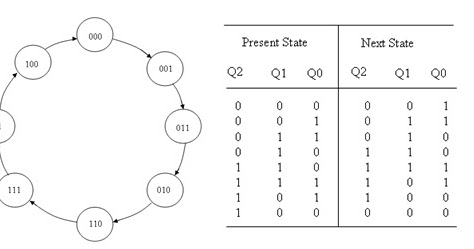

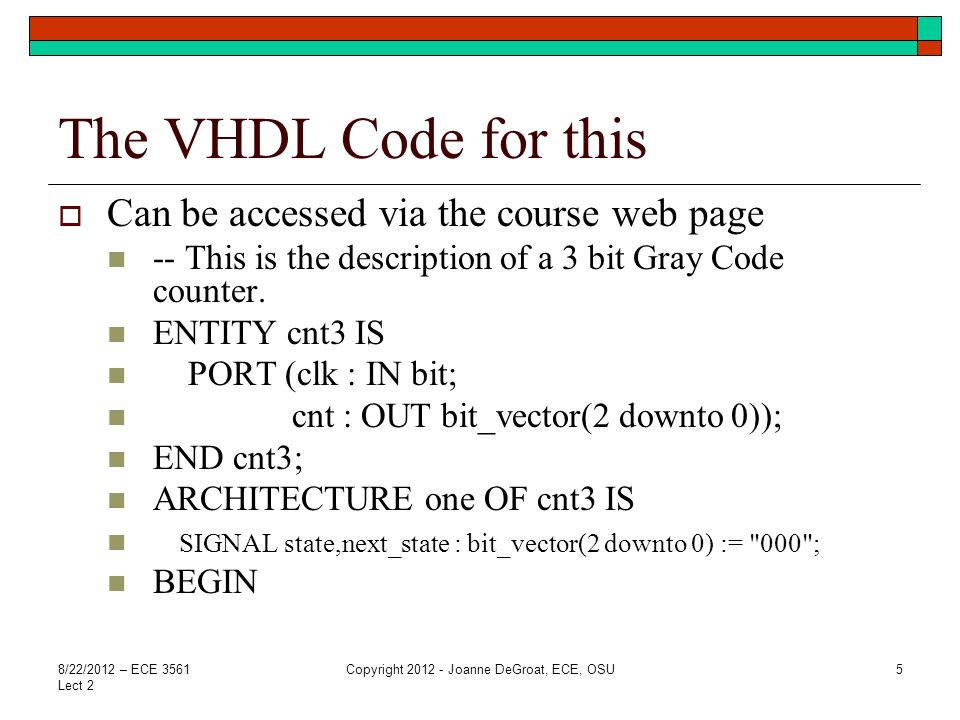

Project 1. Two parts Implement a 3 bit Gray Code Counter Implement a 4-to-1 muxtiplexer Can be done on Altera (Quartis) or Xilinx 8/22/2012 – ECE. - ppt download

Project 1. Two parts Implement a 3 bit Gray Code Counter Implement a 4-to-1 muxtiplexer Can be done on Altera (Quartis) or Xilinx 8/22/2012 – ECE. - ppt download